On August 19, 2023, Shenzhen MilkV Technology Co., Ltd (Milk-V) unveiled the world’s first RISC-V open-source 10-gigabit Ethernet switch - the Milk-V Vega. The core control chip utilizes the FSL1030M network switch chip developed by Wuhan Binary Semiconductor Corporation.

Milk-V Vega is a compact and high-density box-style open-source 10-gigabit Ethernet switch developed by Milk-V for the next-generation network architecture. It offers users a unified platform for various services such as broadband, voice, video, and surveillance, enabling comprehensive coverage of multi-service convergence. Equipped with domestically produced RISC-V high-reliability network switch chips, it significantly simplifies network architecture for enterprises and users, reducing energy consumption costs and operational expenses. It can be widely applied in scenarios including data centers, campuses, medium and large enterprise networks, hotels, research, and education.

Milk-V Vega supports comprehensive Layer 2 network protocol processing capabilities, including L2 bridging, L2 multicast, and storm suppression. It supports VLAN functions based on flows, ports, protocols, and subnets. It also includes STP, RSTP, and QinQ functionalities. Moreover, it provides features such as protection against DOS attacks, black and white lists, and protocol packet filtering. The device supports filters, link aggregation, OAM packet transmission, and port protection functions. It offers ACL capabilities for both inbound and outbound traffic, and also supports Ethernet synchronization and 1588 functions.

Simultaneously, as the world’s first RISC-V open-source 10-gigabit Ethernet switch, Milk-V Vega offers the following features to developers:

- Built on an open-source Linux system, enabling easy secondary development and DIY.

- Open access to openSBI, u-boot, and Linux kernel source code, along with a provided cross-compilation toolchain.

- Equipped with a JTAG interface for convenient low-level development.

- Furnished with RS232 and I2C interfaces, allowing for the connection of other sensors.

- Supports standard 1U server racks, with the capability to install 2 Milk-V Vega units per rack layer.

- Features dual 10-gigabit optical ports + 4 gigabit optical ports + 8 gigabit Ethernet ports, catering to homelab needs.

- Supports remote configuration through WEB and SSH access.

- Provides command-line business configuration for functions such as VLAN setup, port mirroring, MAC address learning, and traffic control.

- Offers interface SDK and API for flexible implementation of business configurations.

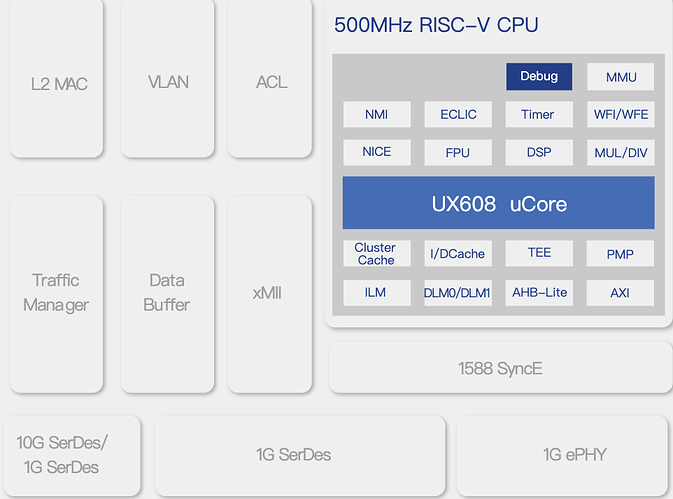

Powered by a domestically designed and manufactured 32G Layer 2 Ethernet switch chip - FSL1030M from China.

The FSL91030M integrates 8 ports of gigabit Ethernet PHY, supporting 10/100/1000BASE-T and 100BASE-FX functionalities. It also incorporates 2 ports of 10G SerDes, enabling support for 1000BASE-X, SGMII, QSGMII, O-USGMII, and 10G BASE-R functionalities. Additionally, it includes 4 ports of 1G SerDes, capable of supporting 1000BASE-X and SGMII functionalities. The combination of 4 ports of 1G SerDes and 4 ports of gigabit Ethernet PHY can be configured as 4 Combo ports. The FSL91030M further supports 2 ports of RGMII/GMII/MII interfaces, serving as expandable management interfaces.

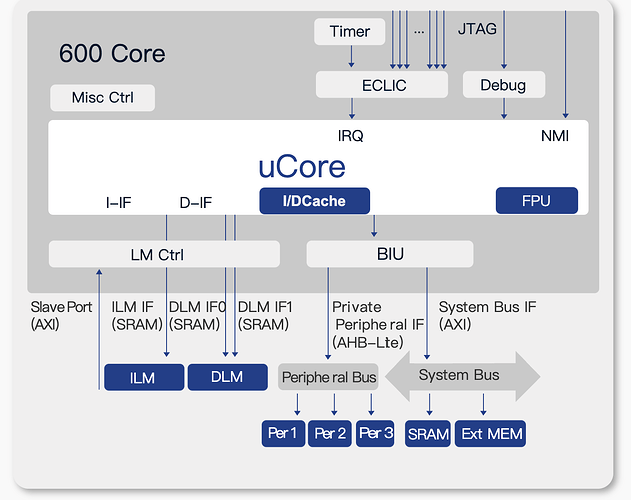

The FSL91030M is built upon Nuclei System Technology Co., Ltd.'s UX608 uCore architecture. It supports the RV32/64 IMACFDPB instruction set and adopts a 6-stage variable-length pipeline architecture to achieve high frequency and performance, meeting the demands of high-performance embedded scenarios. This core supports configurable dual-mode capabilities, allowing for switching between real-time processors and application processors. It also provides a 64-bit AXI system bus interface, AHB-Lite private peripheral interfaces, ILM/DLM interfaces, and slave interfaces.

Configurable on-chip SRAM for instructions and data, along with features like instruction cache (ICache), data cache (DCache), and Cluster Cache, collectively support the enhancement of system performance and efficiency. The core also features a configurable Cache Line Size of 64 bytes, MMU (Memory Management Unit), and single/double precision floating-point extension capabilities. Additionally, configurable PMP (Physical Memory Protection) is used to establish a trusted execution environment, meeting system security requirements.

The core supports standard JTAG and cJTAG debugging interfaces, as well as compile toolchains adhering to the RISC-V standard and Linux/Windows graphical integrated development environments (IDE). These features together constitute the robust feature set of the FSL91030M core, suitable for various application scenarios.

Specification

Milk-V Vega Specification

| Specification | Value |

|---|---|

| CPU Performance | 400MHz |

| Maximum Frame Length | 16,000 bytes |

| On-chip Cache | 1.5MB |

| MAC Address Capacity | 16K |

| VLAN Support | 4K |

| L2 Multicast | 4K |

| Access Control Lists (ACLs) | 256 |

| Meter Minimum Granularity | 8Kbps |

| Flow Policing Entries | 4K |

| Main Controller Power | 4.5W |

| Network Interfaces | |

| - 10GbE SFP+ Optical Ports | 2x |

| - 1GbE SFP Optical Ports | 4x |

| - 1GbE RJ45 Ethernet Ports | 8x |

Network Feature Support

-

Network Redundancy and Protection

- Spanning Tree Protocol (STP), Rapid Spanning Tree Protocol (RSTP)

- 1+1/1:1 Port Protection, Link Aggregation

-

Quality of Service Optimization

- QoS based on 802.1p/DSCP

- VLAN-based translation, L2 multicast

-

Security and Filtering

- Defense against Denial of Service (DoS) attacks, protocol packet filtering

- Black and white lists, IEEE 802.1x

-

Advanced Feature Support

- On-chip packet buffering, ACL, QinQ

- Support for hierarchical Policing

- VLAN based on port, protocol, IP subnet, and flow

-

Flexible Queue Scheduling

- 8 queues per port, multiple scheduling methods (SP/WRR/DWRR)

- Optimized performance with hybrid scheduling methods

-

Traffic Shaping and Control

- Port-based single-rate shaping

- Queue-based dual-rate shaping

- Storm control, L2 bridging

-

Management and Monitoring

- Image and remote configuration

- Hardware periodic transmission of OAM packets

- Synchronous Ethernet (SyncE), 1588 functionality.

About BinarySemi

BinarySemi is a high-tech enterprise primarily engaged in integrated circuit design, research and development, services, and sales. The company’s product portfolio encompasses various fields including network processor chips, Ethernet switch chips and PHY chips, automotive and industrial control MCU chips, hardware security chips, general-purpose analog chips, and more. The company is committed to providing customers with independent and controllable, high-performance, secure, and reliable chip and module solutions.

About Nuclei System Technology

Nuclei System Technology Co., Ltd., founded in 2018, is a China-based specialized provider of RISC-V processor IP and comprehensive solutions. Starting from scratch, the company has developed a complete range of domestically produced and independent RISC-V processor IP products, including N200, N300, N/NX/UX600, N/NX/UX900, covering various application scenarios from low power to high performance. Moreover, it has partnered with heavyweight industry clients to achieve mass production in numerous application areas, spanning across 5G communication, industrial control, artificial intelligence, automotive electronics, Internet of Things, storage, MCU, network security, and more. Presently, they have authorized over 150 formal clients.

About Milk-V

Shenzhen MilkV Technology Co., Ltd, commonly known as Milk-V, brings together a group of passionate and experienced embedded engineers who are filled with boundless enthusiasm and fascination for RISC-V technology. As a company dedicated to the RISC-V open-source ecosystem, Milk-V is committed to sparking a technological revolution and leading global tech trends.

Milk-V remains steadfast in driving the widespread application of RISC-V products, unleashing the creativity of developers, and encouraging their integration into the construction of the RISC-V ecosystem. Milk-V aims not only to showcase the exceptional performance of RISC-V technology to the world but also to collaborate with developers worldwide in exploring the limitless possibilities of future technology.

We anticipate that through the collective efforts of numerous developers, RISC-V products will shine brightly, dazzling like stars in the sky.

For more detail:Milk-V